# **INTERNATIONAL JOURNAL OF RESEARCH IN COMPUTER APPLICATION & MANAGEMENT**

A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories

Indexed & Listed at:

Ulrich's Periodicals Directory ©, ProQuest, U.S.A., EBSCO Publishing, U.S.A., Cabell's Directories of Publishing Opportunities, U.S.A., Open J-Gage, India Ilink of the same is duly available at Inflibret of University Grants Commission (U.G.C.).

Index Copernicus Publishers Panel, Poland with IC Value of 5.09 & number of libraries all around the world. Circulated all over the world & Google has verified that scholars of more than 1866 Cities in 152 countries/territories are visiting our journal on regular basis. Ground Floor, Building No. 1041-C-1, Devi Bhawan Bazar, JAGADHRI – 135 003, Yamunanagar, Haryana, INDIA

http://ijrcm.org.in/

### **CONTENTS**

| Sr.<br>No. | TITLE & NAME OF THE AUTHOR (S)                                                                                                                                                                               | Page N |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| 1.         | FACTORS INFLUENCING KNOWLEDGE SHARING BEHAVIOUR: DEVELOPING A THEORETICAL FRAMEWORK<br>SOOFI ANWAR & DR. K. DURGA PRASAD                                                                                     | 1      |  |  |  |

| <b>2</b> . | THE IMPACT OF DIRECT AND INDIRECT FACTORS INFLUENCING BRAND EQUITY FOR ONLINE COMPANIES                                                                                                                      | 4      |  |  |  |

| 3.         | SEYED ALIAKBAR AHMADI, MOHAMMADREZA DARAEI & EHSAN POUSTIAN<br>INTEGRATION OF TECHNOLOGY IN TEACHING SENIOR HIGH SCHOOL SOCIAL STUDIES: THE COMPUTER ASSISTED INSTRUCTION EFFECT ON<br>STUDENTS' PERFORMANCE | 9      |  |  |  |

|            | PAUL DELA AHIATROGAH, BRANDFORD BERVELL & AUGUSTINE YAKUBU                                                                                                                                                   |        |  |  |  |

| 4.         | USING THE ANALYTIC HIERARCHY PROCESS TO ENHANCE PARTICIPATORY DECISION-MAKING IN MULTI-STAKEHOLDER INFRASTRUCTURE<br>PROJECTS: A PIPELINE PROJECT CASE STUDY<br>VICTOR. A. AKUJURU & BANKOLE. O. AWUZIE      | 16     |  |  |  |

| 5.         | PRACTICAL IMPLEMENTATION OF THE MODEL FOR 'ORGANIZING, MEASURING, ANALYZING STUDENTS' KNOWLEDGE AND<br>PERFORMANCE'<br>ROY MATHEW                                                                            | 24     |  |  |  |

| 5.         | DETERMINANTS OF SMALLHOLDERS' PARTICIPATION IN LOCAL BASED SEED PRODUCTION SYSTEM: THE CASE OF ONION SEED IN EAST<br>SHOA ZONE OF THE OROMIYA NATIONAL REGIONAL STATE, ETHIOPIA                              | 34     |  |  |  |

| 7.         | FREAW DEMISE & DAWIT ALEMU COINTEGRATION OF KARACHI STOCK MARKET WITH OTHER ASIAN STOCK MARKETS FELINIDA AKRAMA AISUA AKRAMA SUANIZA ARELIAD & MAZUAR JORAL                                                  | 43     |  |  |  |

| 3.         | FEHMIDA AKRAM, AISHA AKRAM, SHANZA ARSHAD & MAZHAR IQBAL<br>SURVEY ON FACTORS INFLUENCING THE PERFORMANCE OF PLM SYSTEM IN AUTO INDUSTRY                                                                     | 47     |  |  |  |

|            | M. S. GOPINATHA, DR. VISHNUKANTH S. CHATPALLI & DR. K.S. SRIDHAR                                                                                                                                             |        |  |  |  |

| 9.         | A STUDY ON QUALITY WORK LIFE WITH REFERENCE TO ENGINEERING COLLEGES AT BANGALORE<br>SUNIL RASHINKAR, SRI HARI.V, DR.SREENIVAS.D.L, LAKSHMI NARAYANA.K & SHAZIA KAUSAR                                        | 53     |  |  |  |

| 0.         | POWER & AREA EFFICIENT ROUTER IN 2-D MESH NETWORK-ON-CHIP USING LOW POWER METHODOLOGY – GATE LEVEL POWER<br>OPTIMIZATION<br>SUDHIR N. SHELKE & PRAMOD B. PATIL                                               | 61     |  |  |  |

| 1.         | THE STATISTICAL ANALYSIS OF STRUCTURE OF MANUFACTURING SECTOR – WITH SPECIAL REFERENCE TO BANGALORE INDUSTRIAL<br>REGION<br>A. T. SRINIVASA & DR. MUNIVENKATAPPA                                             | 68     |  |  |  |

| <b>2</b> . | A STUDY ON CONSUMER PERCEPTION OF TATA LPT 3118 12 TYRE VEHICLE OVER 10 TYRE VEHICLES WITH REFERENCE TO THOOTHUKUDI<br>S. JEBASEELI NOVALEENA & DR. A. RANGAWSAMY                                            | 75     |  |  |  |

| <b>3</b> . | EMPLOYEE ABSENTEEISM IN HEALTH CARE INDUSTRY: A CONCERN FOR THE ORGANIZATION<br>DR. C. SWARNALATHA & T.S. PRASANNA                                                                                           | 83     |  |  |  |

| 4.         | WEB CONTENT TRUST ASSESSMENT MODEL USING ADVANCE WEB MINING TECHNIQUES<br>KETAN.J.PATEL, KETAN.D.PATEL & DR. V. R. RATHOD                                                                                    | 86     |  |  |  |

| 5.         | PERFORMANCE OF PROFITABILITY MANAGEMENT IN AMARA RAJA BATTERIES LIMITED", TIRUPATI - AN EVALUATION<br>K.KALYANI & DR. P. MOHAN REDDY                                                                         | 89     |  |  |  |

| 6.         | AN ELABORATION LIKELIHOOD MODEL APPROACH TO PACKAGING AND CHILD-PARENT INTERACTION<br>SURAJ KUSHE SHEKHAR & DR. P.T RAVEENDRAN                                                                               | 93     |  |  |  |

| 7.         | RELATIONSHIP OF FINANCIAL REPORTING QUALITY WITH SALES VOLATILITY AND BOOK TO MARKET VALUE<br>MOHAMMAD REZA RAZDAR & DR. B. H. SURESH                                                                        | 97     |  |  |  |

| 8.         | WORKING CAPITAL MANAGEMENT IN MANUFACTURING INDUSTRY: A STUDY WITH REFERENCE TO SELECTED MANUFACTURING<br>INDUSTRIES IN INDIA<br>KUSHALAPPA. S & SHARMILA KUNDER                                             | 10     |  |  |  |

| 9.         | TALENT ACQUISITION AND RETENTION: A STUDY IN INDIAN SMALL AND MEDIUM ENTERPRISES                                                                                                                             | 10     |  |  |  |

| 0.         | DR. SNIGDHARANI MISHRA & JASMINE T. JHA MONITORING SYSTEM FOR TERRORISTS AND DANGEROUS PRISONERS                                                                                                             | 11     |  |  |  |

| 1.         | DR. PRAMOD BUBNA TRENDS OF FOREIGN DIRECT INVESTMENT IN INDIA                                                                                                                                                | 114    |  |  |  |

| 2.         | DR. KARAMVIR SINGH SHEOKAND, PRIYANKA & RAJESH BHARDWAJ CONCURRENCY CONTROL IN DBMS WITH TIMESTAMPS                                                                                                          | 11     |  |  |  |

| 3.         | GEETIKA A STUDY ON PERFORMANCE MANAGEMENT SYSTEM (PMS) WITH SPECIAL REFERENCE TO COTELLIGENT                                                                                                                 | 12     |  |  |  |

| 4.         | <i>P SWETHA</i><br>AN ANALYSIS OF CHILD'S INFLUENCE IN CHOOSING THE SNACKS ITEMS WITH SPECIAL REFERENCES TO SIVAKASI AREA IN TAMILNADU                                                                       | 12     |  |  |  |

| 5.         | T. DHANALAKSHMI MEASURING SERVICE QUALITY OF RAILWAY PLATFORMS IN INDIA: A CASE-STUDY OF EAST-COAST RAILWAYS                                                                                                 |        |  |  |  |

| 6.         | DR. SRINIBASH DASH, SRI SISIR RANJAN DASH & SRI SUBRAT KUMAR PRADHAN A COMPARATIVE STUDY OF FINANCIAL STATEMENT OF DISTRICT CO-OPERATIVE DAIRIES OF NORTH GUJARAT                                            |        |  |  |  |

| 7.         | PATEL RAJESHKUMAR G., PRAJAPATI RASIKBHAI I. & PATEL NITINKUMAR P. WORLD WIDE MIDDLE WARE TECHNOLOGIES                                                                                                       |        |  |  |  |

| 8.         | M.DHANAMALAR & B.AYSHWARYA CRITICAL FACTORS FOR SUCCESSFUL SC COLLABORATION: AN INTERPRETIVE STRUCTURAL MODELING APPROACH                                                                                    |        |  |  |  |

| 9.         | KAUSTUBH JOSHI & ANIKET JADHAV<br>AN EMPIRICAL INVESTIGATION OF INVENTORY MANAGEMENT PRACTICES OF MYSORE PAPER MILLS LIMITED BHADRAVATHI – A CASE<br>STUDY                                                   | 15(    |  |  |  |

| 0.         | BASAVARAJAPPA M T A STUDY ON PERFORMANCE OF MOBILE BAKING SERVICES AND MODELS IN INDIA M CANCUL NAIDU                                                                                                        | 156    |  |  |  |

|            | M.GANGU NAIDU REQUEST FOR FEEDBACK                                                                                                                                                                           | 161    |  |  |  |

A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories

## <u>CHIEF PATRON</u>

PROF. K. K. AGGARWAL

Chancellor, Lingaya's University, Delhi Founder Vice-Chancellor, Guru Gobind Singh Indraprastha University, Delhi Ex. Pro Vice-Chancellor, Guru Jambheshwar University, Hisar

LATE SH. RAM BHAJAN AGGARWAL Former State Minister for Home & Tourism, Government of Haryana Former Vice-President, Dadri Education Society, Charkhi Dadri Former President, Chinar Syntex Ltd. (Textile Mills), Bhiwani

## CO-ORDINATOR

DR. SAMBHAV GARG Faculty, M. M. Institute of Management, MaharishiMarkandeshwarUniversity, Mullana

## <u>ADVISORS</u>

DR. PRIYA RANJAN TRIVEDI Chancellor, The Global Open University, Nagaland PROF. M. S. SENAM RAJU Director A. C. D., School of Management Studies, I.G.N.O.U., New Delhi PROF. S. L. MAHANDRU Principal (Retd.), MaharajaAgrasenCollege, Jagadhri

## **EDITOR**

PROF. R. K. SHARMA Professor, Bharti Vidyapeeth University Institute of Management & Research, New Delhi

## EDITORIAL ADVISORY BOARD

DR. RAJESH MODI Faculty, YanbulndustrialCollege, Kingdom of Saudi Arabia PROF. PARVEEN KUMAR Director, M.C.A., Meerut Institute of Engineering & Technology, Meerut, U. P. PROF. H. R. SHARMA Director, Chhatarpati Shivaji Institute of Technology, Durg, C.G. PROF. MANOHAR LAL Director & Chairman, School of Information & Computer Sciences, I.G.N.O.U., New Delhi PROF. ANIL K. SAINI Chairperson (CRC), Guru Gobind Singh I. P. University, Delhi PROF. R. K. CHOUDHARY Director, Asia Pacific Institute of Information Technology, Panipat DR. ASHWANI KUSH Head, Computer Science, UniversityCollege, KurukshetraUniversity, Kurukshetra **DR. BHARAT BHUSHAN**

Head, Department of Computer Science & Applications, Guru Nanak Khalsa College, Yamunanagar

**DR. VIJAYPAL SINGH DHAKA**

Dean (Academics), Rajasthan Institute of Engineering & Technology, Jaipur

### **DR. SAMBHAVNA**

Faculty, I.I.T.M., Delhi

**DR. MOHINDER CHAND**

Associate Professor, KurukshetraUniversity, Kurukshetra

**DR. MOHENDER KUMAR GUPTA**

Associate Professor, P.J.L.N.GovernmentCollege, Faridabad

### **DR. SAMBHAV GARG**

Faculty, M. M. Institute of Management, MaharishiMarkandeshwarUniversity, Mullana

### **DR. SHIVAKUMAR DEENE**

Asst. Professor, Dept. of Commerce, School of Business Studies, Central University of Karnataka, Gulbarga

**DR. BHAVET**

Faculty, M. M. Institute of Management, MaharishiMarkandeshwarUniversity, Mullana

## ASSOCIATE EDITORS

PROF. ABHAY BANSAL Head, Department of Information Technology, Amity School of Engineering & Technology, Amity University, Noida PROF. NAWAB ALI KHAN Department of Commerce, AligarhMuslimUniversity, Aligarh, U.P. ASHISH CHOPRA Sr. Lecturer, Doon Valley Institute of Engineering & Technology, Karnal

## TECHNICAL ADVISOR

**AMITA** Faculty, Government M. S., Mohali

## FINANCIAL ADVISORS

DICKIN GOYAL Advocate & Tax Adviser, Panchkula

NEENA

Investment Consultant, Chambaghat, Solan, Himachal Pradesh

## LEGAL ADVISORS

JITENDER S. CHAHAL Advocate, Punjab & Haryana High Court, Chandigarh U.T. CHANDER BHUSHAN SHARMA Advocate & Consultant, District Courts, Yamunanagar at Jagadhri

**SURENDER KUMAR POONIA**

DATED:

v

## **CALL FOR MANUSCRIPTS**

We invite unpublished novel, original, empirical and high quality research work pertaining to recent developments & practices in the area of Computer, Business, Finance, Marketing, Human Resource Management, General Management, Banking, Insurance, Corporate Governance and emerging paradigms in allied subjects like Accounting Education; Accounting Information Systems; Accounting Theory & Practice; Auditing; Behavioral Accounting; Behavioral Economics; Corporate Finance; Cost Accounting; Econometrics; Economic Development; Economic History; Financial Institutions & Markets; Financial Services; Fiscal Policy; Government & Non Profit Accounting; Industrial Organization; International Economics & Trade; International Finance; Macro Economics; Micro Economics; Monetary Policy; Portfolio & Security Analysis; Public Policy Economics; Real Estate; Regional Economics; Tax Accounting; Advertising & Promotion Management; Business Education; Management Information Systems (MIS); Business Law, Public Responsibility & Ethics; Communication; Direct Marketing; E-Commerce; Global Business; Health Care Administration; Labor Relations & Human Resource Management; Marketing Research; Marketing Theory & Applications; Non-Profit Organizations; Office Administration/Management; Operations Research/Statistics; Organizational Behavior & Theory; Organizational Development; Production/Operations; Public Administration; Purchasing/Materials Management; Retailing; Sales/Selling; Services; Small Business Entrepreneurship; Strategic Management Policy; Technology/Innovation; Tourism, Hospitality & Leisure; Transportation/Physical Distribution; Algorithms; Artificial Intelligence; Compilers & Translation; Computer Aided Design (CAD); Computer Aided Manufacturing; Computer Graphics; Computer Organization & Architecture; Database Structures & Systems; Digital Logic; Discrete Structures; Internet; Management Information Systems; Modeling & Simulation; Multimedia; Neural Systems/Neural Networks; Numerical Analysis/Scientific Computing; Object Oriented Programming; Operating Systems; Programming Languages; Robotics; Symbolic & Formal Logic and Web Design. The above mentioned tracks are only indicative, and not exhaustive.

Anybody can submit the soft copy of his/her manuscript **anytime** in M.S. Word format after preparing the same as per our submission guidelines duly available on our website under the heading guidelines for submission, at the email address: <u>infoircm@gmail.com</u>.

## **GUIDELINES FOR SUBMISSION OF MANUSCRIPT**

#### 1. COVERING LETTER FOR SUBMISSION:

*THE EDITOR* IJRCM

Subject: SUBMISSION OF MANUSCRIPT IN THE AREA OF

(e.g. Finance/Marketing/HRM/General Management/Economics/Psychology/Law/Computer/IT/Engineering/Mathematics/other, please specify)

#### DEAR SIR/MADAM

Please find my submission of manuscript entitled '\_\_\_\_\_\_\_ virgent control of the publication in your journals.

I hereby affirm that the contents of this manuscript are original. Furthermore, it has neither been published elsewhere in any language fully or partly, nor is it under review for publication elsewhere.

I affirm that all the author (s) have seen and agreed to the submitted version of the manuscript and their inclusion of name (s) as co-author (s).

Also, if my/our manuscript is accepted, I/We agree to comply with the formalities as given on the website of the journal & you are free to publish our contribution in any of your journals.

#### NAME OF CORRESPONDING AUTHOR:

Designation: Affiliation with full address, contact numbers & Pin Code: Residential address with Pin Code: Mobile Number (s): Landline Number (s): E-mail Address: Alternate E-mail Address:

NOTES:

2

- a) The whole manuscript is required to be in **ONE MS WORD FILE** only (pdf. version is liable to be rejected without any consideration), which will start from the covering letter, inside the manuscript.

- b) The sender is required to mention the following in the SUBJECT COLUMN of the mail: New Manuscript for Review in the area of (Finance/Marketing/HRM/General Management/Economics/Psychology/Law/Computer/IT/ Engineering/Mathematics/other, please specify)

- C) There is no need to give any text in the body of mail, except the cases where the author wishes to give any specific message w.r.t. to the manuscript.

- d) The total size of the file containing the manuscript is required to be below **500 KB**.

- e) Abstract alone will not be considered for review, and the author is required to submit the complete manuscript in the first instance.

- f) The journal gives acknowledgement w.r.t. the receipt of every email and in case of non-receipt of acknowledgment from the journal, w.r.t. the submission of manuscript, within two days of submission, the corresponding author is required to demand for the same by sending separate mail to the journal.

- MANUSCRIPT TITLE: The title of the paper should be in a 12 point Calibri Font. It should be bold typed, centered and fully capitalised.

- 3. AUTHOR NAME (S) & AFFILIATIONS: The author (s) full name, designation, affiliation (s), address, mobile/landline numbers, and email/alternate email address should be in italic & 11-point Calibri Font. It must be centered underneath the title.

- 4. **ABSTRACT**: Abstract should be in fully italicized text, not exceeding 250 words. The abstract must be informative and explain the background, aims, methods, results & conclusion in a single para. Abbreviations must be mentioned in full.

- 5. **KEYWORDS:** Abstract must be followed by a list of keywords, subject to the maximum of five. These should be arranged in alphabetic order separated by commas and full stops at the end.

- 6. **MANUSCRIPT**: Manuscript must be in <u>BRITISH ENGLISH</u> prepared on a standard A4 size <u>PORTRAIT SETTING PAPER</u>. It must be prepared on a single space and single column with 1" margin set for top, bottom, left and right. It should be typed in 8 point Calibri Font with page numbers at the bottom and centre of every page. It should be free from grammatical, spelling and punctuation errors and must be thoroughly edited.

- 7. **HEADINGS**: All the headings should be in a 10 point Calibri Font. These must be bold-faced, aligned left and fully capitalised. Leave a blank line before each heading.

- 8. SUB-HEADINGS: All the sub-headings should be in a 8 point Calibri Font. These must be bold-faced, aligned left and fully capitalised.

- 9. **MAIN TEXT**: The main text should follow the following sequence:

INTRODUCTION

**REVIEW OF LITERATURE**

**NEED/IMPORTANCE OF THE STUDY**

STATEMENT OF THE PROBLEM

OBJECTIVES

HYPOTHESES

RESEARCH METHODOLOGY

RESULTS & DISCUSSION

FINDINGS

**RECOMMENDATIONS/SUGGESTIONS**

CONCLUSIONS

SCOPE FOR FURTHER RESEARCH

ACKNOWLEDGMENTS

REFERENCES

#### APPENDIX/ANNEXURE

It should be in a 8 point Calibri Font, single spaced and justified. The manuscript should preferably not exceed 5000 WORDS.

- 10. FIGURES & TABLES: These should be simple, crystal clear, centered, separately numbered &self explained, and titles must be above the table/figure. Sources of data should be mentioned below the table/figure. It should be ensured that the tables/figures are referred to from the main text.

- 11. EQUATIONS: These should be consecutively numbered in parentheses, horizontally centered with equation number placed at the right.

- 12. **REFERENCES:** The list of all references should be alphabetically arranged. The author (s) should mention only the actually utilised references in the preparation of manuscript and they are supposed to follow **Harvard Style of Referencing**. The author (s) are supposed to follow the references as per the following:

- All works cited in the text (including sources for tables and figures) should be listed alphabetically.

- Use (ed.) for one editor, and (ed.s) for multiple editors.

- When listing two or more works by one author, use --- (20xx), such as after Kohl (1997), use --- (2001), etc, in chronologically ascending order.

- Indicate (opening and closing) page numbers for articles in journals and for chapters in books.

- The title of books and journals should be in italics. Double quotation marks are used for titles of journal articles, book chapters, dissertations, reports, working

papers, unpublished material, etc.

- For titles in a language other than English, provide an English translation in parentheses.

- The location of endnotes within the text should be indicated by superscript numbers.

PLEASE USE THE FOLLOWING FOR STYLE AND PUNCTUATION IN REFERENCES:

### BOOKS

- Bowersox, Donald J., Closs, David J., (1996), "Logistical Management." Tata McGraw, Hill, New Delhi.

- Hunker, H.L. and A.J. Wright (1963), "Factors of Industrial Location in Ohio" Ohio State University, Nigeria.

### CONTRIBUTIONS TO BOOKS

Sharma T., Kwatra, G. (2008) Effectiveness of Social Advertising: A Study of Selected Campaigns, Corporate Social Responsibility, Edited by David Crowther & Nicholas Capaldi, Ashgate Research Companion to Corporate Social Responsibility, Chapter 15, pp 287-303.

### JOURNAL AND OTHER ARTICLES

Schemenner, R.W., Huber, J.C. and Cook, R.L. (1987), "Geographic Differences and the Location of New Manufacturing Facilities," Journal of Urban Economics, Vol. 21, No. 1, pp. 83-104.

### CONFERENCE PAPERS

Garg, Sambhav (2011): "Business Ethics" Paper presented at the Annual International Conference for the All India Management Association, New Delhi, India, 19–22 June.

### UNPUBLISHED DISSERTATIONS AND THESES

Kumar S. (2011): "Customer Value: A Comparative Study of Rural and Urban Customers," Thesis, KurukshetraUniversity, Kurukshetra.

### ONLINE RESOURCES

Always indicate the date that the source was accessed, as online resources are frequently updated or removed.

### WEBSITES

Garg, Bhavet (2011): Towards a New Natural Gas Policy, Political Weekly, Viewed on January 01, 2012 http://epw.in/user/viewabstract.jsp

### **INTERNATIONAL JOURNAL OF RESEARCH IN COMPUTER APPLICATION & MANAGEMENT**

A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories

### http://ijrcm.org.in/

### POWER & AREA EFFICIENT ROUTER IN 2-D MESH NETWORK-ON-CHIP USING LOW POWER METHODOLOGY – GATE LEVEL POWER OPTIMIZATION

### SUDHIR N. SHELKE ASST. PROFESSOR DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION ENGINEERING J.D. COLLEGE OF ENGINEERING NAGPUR

### PRAMOD B. PATIL PRINCIPAL J.D. COLLEGE OF ENGINEERING NAGPUR

### ABSTRACT

Network-on-Chip (NoC) is the interconnection platform that answers the requirements of the modern on-Chip design. Small optimizations in NoC router architecture can show a significant improvement in the overall performance of NoC based systems. Power consumption, area overhead and the entire NoC performance is influenced by the router buffers. Resource sharing for on-chip network is critical to reduce the chip area and power consumption. An area efficient implementation of a routing node for a NoC is presented. Of the four components of routing node, the input block (mainly consisting of buffers) and scheduler have been modified to save area requirements. The other two components of the routing node take up negligible area in comparison. The use of custom SRAM in place of synthesizable flip flops in the input block has resulted in a saving of over 26% of the silicon area and power optimization is 65% when operated at 16 ns clock. Clock gating is an important high-level technique for reducing the power consumption of a design. Clock gating reduces the clock network power dissipation, relaxes the datapath timing, and reduces routing congestion by eliminating feedback multiplexer loops. For designs that have large multi-bit registers, clock gating gate level can save power and reduce the number of gates in the design. In our design case, it has been further observed that the power optimization with clock gating techniques at gate level saves 67.38%, of power while 32.62 %, 32.71 % & 30.28% silicon area has been saved.

### **KEYWORDS**

Clock Gating, Network-on-Chip, Router, SRAM, RTL.

### **1. INTRODUCTION**

ver-increasing requirements on electronic systems are one of the key factors for evolution of the integrated circuit technology. Multiprocessing is the solution to meet the requirements of upcoming applications. Multiprocessing over heterogeneous functional units require efficient on chip communication. [1] [2].

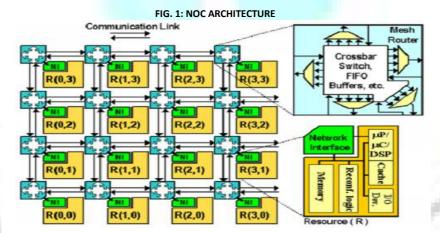

Network-on-Chip (NoC) is a general purpose on-chip communication concept that offers high throughput, which is the basic requirement to deal with complexity of modern systems, as shown in Fig 1.

All links in NoC can be simultaneously used for data transmission, which provides a high level of parallelism and makes it attractive to replace the typical communication architectures like shared buses or point-to-point dedicated wires.

Apart from throughput, NoC platform is scalable and has the potential to keep up with the pace of technology advances [3]. But all these enhancements come at the expense of area and power. In the RAW multiprocessor system, interconnection network consumes 36% of the total chip power [4]. A typical NoC system consists of processing elements (PEs), network interfaces (NIs), routers and channels. The router further contains scheduler, switch and buffers. Buffers consume the 64% of the total node (router + link) leakage power for all process technologies, which makes it the largest power consumer in any NoC system. [5]. Moreover, buffers are dominant for dynamic energy consumption [6].

### 2. NoC ARCHITECTURE

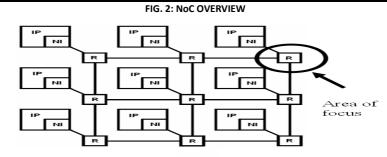

Network-on-Chip has been proposed on various topologies [7] - [10]. A simple NoC architecture consists of three components: the routing nodes, the links, and network interfaces (or network adapters in some literature), as shown in Fig. 2.

Routers direct data over several links (hops). Topology defines their logical lay-out (connections) whereas floorplan defines the physical layout. The function of a network interface (adapter) is to decouple computation (the resources) from communication (the network). Routing decides the path taken from source to the destination whereas switching and flow control policies define the timing of transfers. Task scheduling refers to the order in which the application tasks are executed and task mapping defines which processing element (PE) executes certain task. IP mapping, on the other hand, defines how PEs and other resources are connected to the NoC [11].

The major goal of communication-centric design and NoC paradigm is to achieve greater design productivity and performance by handling the increasing parallelism, manufacturing complexity, wiring problems, and reliability. The three critical challenges for NoC. are: power, area, latency, and CAD compatibility. [12].The key research areas in network-on-chip design [13] [14].are as:

• Communication infrastructure: topology and link optimization, buffer sizing, floorplanning, clock domains, power.

· Communication paradigm: routing, switching, flow control, quality-of-service, network interfaces

• Application mapping: task mapping/scheduling and IP component mapping.

All of these challenges result in area, power, and performance tradeoffs [13]. Area and power can be estimated from hardware requirements. Performance is generally estimated using analytical model.

This paper proposes the area and power efficient design of the router as it is the most redundant component which is equal to the no. of PEs on one kind of NoC, as shown in Fig. 2.

### **3. PROBLEM STATEMENT**

The implementation of network-on-chip presents certain challenges. Two of the most critical design metrics for networks-on-chip are area requirements and power consumption. Due to the fact that die area per wafer of silicon is limited, the NoC implementation should be carried out using an approach that minimizes area requirement. Also due to likelihood of most SoCs being implemented in battery powered devices, power consumption of the NoC should also be as low as possible. Usually, reduction in area results in a saving in power requirements due to the fact a smaller area is achieved using fewer components on-chip. Fewer components on-chip will consumeless power compared to architecture requiring more components on-chip.

Standard-cell based ASIC design methodology is the fastest approach available in the design of complex digital circuits. However, the performance of digital systems can be enhanced by making use of custom IP cores to replace some of the standard-cell components. This performance enhancement comes at the price of increased design time and effort, but is preferred for maximizing performance.

### 4. DESIGN AND IMPLEMENTATION OF PROPOSED TASK

Given an existing implementation of a routing node for on-chip networks, it is the goal of this work to present a modified implementation of the routing node to minimize the area requirements and as a result lower the power requirement.

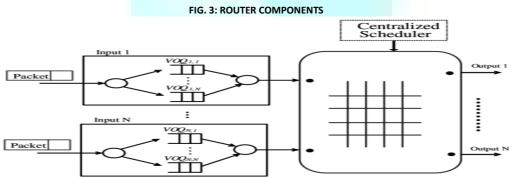

The routing node consists of four basic components: the input ports, the output ports, the crossbar switch, and the scheduler. The components arranged in decreasing order of size are the input blocks, the scheduler, the output blocks, and the crossbar switch as shown in Fig 3.

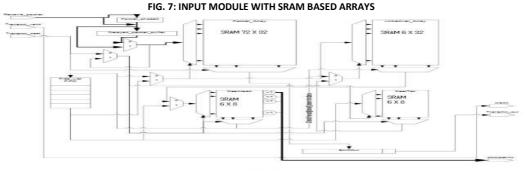

The primary function of the input block is to store incoming packets before they can be routed to their respective output ports. Hence, the majority of the area of the input blocks is used by memory elements. The existing design employs DFF (D flip-flop) elements for memory storage. The modified input block will be based on SRAM memory cells. SRAM memory cells provide the fastest and most compact means of on-chip storage. DRAM is much more compact but suffers in terms of speed due to the constant refresh signals required to maintain memory content. In high performance CPU architectures, memory is implemented as on-chip SRAM to achieve the best possible performance.

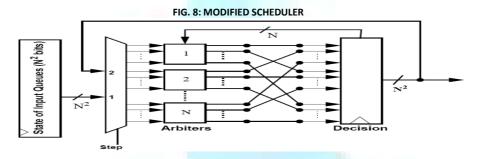

The function of the scheduler is to arbitrate between conflicting requests for access to the crossbar switch shared medium. The existing scheduler architecture is based on a symmetric implementation of round-robin like algorithm requiring one set of grant arbiters and one set of accept arbitres to perform arbitration. The modified design uses the concept of folding to reduce the area of the scheduler by removing one set of arbitres and using the remaining set of arbitres to perform both grant and accept arbitration in a time multiplexed fashion.

The design of the modified routing node is implemented using standard cell based VLSI flow with provision for custom IP core inclusion. The Synopsis tool chain is used to implement the design from RTL coding to synthesis and place and route.

Design verification is carried out using hierarchical functional simulation at each level of the design flow. Also, static timing analysis is used to verify timing closure in the final design layout.

Area and power are two important parameters which need to be optimized for better NoC performance. The NoC consists of three basic components which are the routing node, the routing links, and network interfaces. Optimization of the routing nodes will lead to improvement in the area and the power requirements of the NoC, as it is the most redundant component which lies in association with every processing element in SOC. Thus, the aim of this work is to present a modified architecture of the routing node to achieve higher area and power efficiency using changes at the RTL architecture level and use of custom IP to boost the performance of standard-cell based ASIC design.

### 5. THE PROPOSED ROUTER ARCHITECTURE

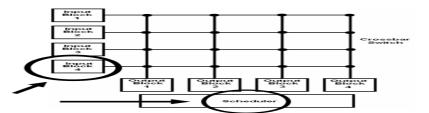

The routing node configuration shown in Fig.4 is 4x4. It is based on a 2D mesh NoC topology where each routing node is connected to four other routing nodes. The NOC infrastructure includes components responsible for packetization, transmission, and de-packetization of data. These components, respectively, are the

INTERNATIONAL JOURNAL OF RESEARCH IN COMPUTER APPLICATION & MANAGEMENT A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories http://ijrcm.org.in/

### VOLUME NO. 2 (2012), ISSUE NO. 12 (DECEMBER)

NI, the VC router, and the links. These components are repeated for every grid element in NOC. So, if we consider a NOC with 3×3 mesh network, then it will have nine sets of components of NI, VC router and links. It can be clearly seen that these components will occupy a significant amount of silicon space on the chip and therefore the cost and the power consumption of the chip would increase. However, it must be noted that serial packet-based communication will still remain an optimum solution as compared to a bus-based system in terms of the power consumption and will reduce the cost of system design in the longer run due to the potential for reuse.

#### FIG. 4: 4x4 ROUTING NODE

### 6. AREA OF FOCUS

The design of the proposed router has been carried out as follows]: 6.1 PROPOSED SWITCHING TECHNIQUE

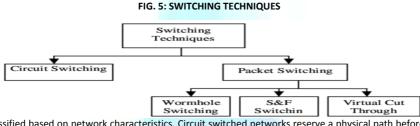

Switching techniques can be classified based on network characteristics. Circuit switched networks reserve a physical path before transmitting the data packets, while packet switched networks transmit the packets without reserving the entire path. Packet switched networks can further be classified as Wormhole, Store and Forward (S&F), and Virtual Cut through Switching (VCT) networks as shown in Fig. 5. In Wormhole switching networks, only the header flit experiences latency. Other flits belonging to the same packet simply follow the path taken by the header flit. If the header flit is blocked then the entire packet is blocked. It does not require any buffering of the packet. Therefore, the size of the chip drastically reduces. However, the major drawback of this switching technique is a higher latency. Thus, it is not a suitable switching technique for real-time data transfers.

S&F switching forwards a packet only when there is enough space available in the receiving buffer to hold the entire packet. Thus, there is no need for dividing a packet into flits. This reduces the overhead, as it does not require circuits such as a flit builder, a flit decoder, a flit stripper and a flit sequencer. Store and forward is the easiest policy in terms of implementation complexity. So this implementation is based on store and forward switching.

#### 6.2. PROPOSED FLOW CONTROL MECHANISM

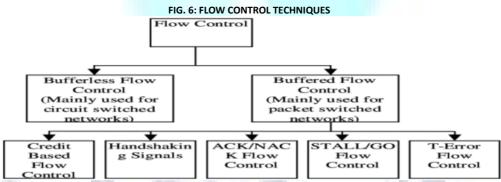

Flow control determines how network resources, such as channel bandwidth, buffer capacity, and control state, are allocated to a packet traversing the network. The flow control may be buffered or buffer less as shown in Fig.6. The Buffer less Flow Control has more latency and fewer throughputs than the Buffered Flow Control. The Buffered Flow Control can be classified further as:

In Credit Based Flow Control, an upstream node keeps count of data transfers, and thus the available free slots are termed as credits. Once the transmitted data packet is either consumed or further transmitted, a credit is sent back and used [15] [16].

In Handshaking Signal Based Flow Control, a VALID signal is sent whenever a sender transmits any flit. The receiver acknowledges by asserting a VALID signal after consuming the data flit and used in SoCIN NOC implementation [17].

To minimize the chances of dropped packets at the receiving end, the credit based flow control mechanism has been incorporated wherein only those output IP blocks take part in the scheduling that has some credit. In addition to this, every input block maintains packet array and the linked list array to maintain the proper flow so as to avoid the out of order delivery.

### 6.3. PROPOSED BUFFER IMPLEMENTATION IN THE DESIGN OF ROUTER

A higher buffer capacity and a larger number of virtual channels in the buffer will reduce network contention, thereby reducing latency. However, buffers are area hungry, and their use needs to be carefully directed [18] [19] therefore proposed a simple implementation of a buffer architecture for NOC buffers using 0.18 µm technology to estimate the cost and area of buffers needed for NOC. Also proposed the trade-off between buffer size and channel bandwidth to secure constant latency and concluded that increasing the channel bandwidth is preferable to reducing the latency in NOC.

The input block consists of six major components: the packet array, the linked list array, the destination head array, the destination tail array, the free-list FIFO, and a shift register. Four of these six components are conventional memory elements. In a standard cell based design, memory elements are realized using D flip flops in the standard SYNOPSYS Library. If we consider a NAND gate implementation of a D flip flop with no RESET or SET inputs it requires 28 MOS transistors to realize one D flip flop [20]. A more area efficient implementation of memory is through the use of SRAM cells. Each SRAM cell is implemented using 6 transistors. Therefore, memory realization using SRAM is more efficient compared to D flip flops. However, standard cell based approach to ASIC design does provide SRAM standard cells because of the many possible configurations of width and depth. SRAM design is carried out using full custom approach to ASIC design, D flip flops can be replaced by SRAM, improving the area efficiency

of the input block. Full custom design of SRAMs has been carried out by MILKYWAY of SYNOPSY, while physical implementation of the input module with SRAMs has been carried out by IC Compiler of SYNOPSY.

### 6.4. PROPOSED SCHEDULER IN THE DESIGN

The scheduler was modified using a folding approach due to the regular structure and placement of the arbiters. The modified scheduler is as shown in Fig, 8. Each arbiter in the modified scheduler now has to generate both grant and accept signals in a time multiplexed fashion. The arbiter is modified to hold both grant and accept pointers for successive time slots.

The proposed scheduler belongs to a Router in 2D Mesh NOC design. So here the value of N is 4.

### 7. INTRODUCTION TO CLOCK GATING

Clock gating [21] - [24] applies to synchronous load-enable registers, which are groups of flip-flops that share the same clock and synchronous control signals and that are inferred from the same HDL variable. Synchronous control signals include synchronous load-enable, synchronous set, synchronous reset, and synchronous toggle. The registers are implemented by Design Compiler by use of feedback loops. However, these registers maintain the same logic value through multiple cycles and unnecessarily use power. Clock gating saves power by eliminating the unnecessary activity associated with reloading register banks. Designs that benefit most from clock gating are those with low-throughput data paths. Designs that benefit less from RTL clock gating include designs with finite state machines or designs with throughput-of-one data paths.

Power Compiler allows performing clock gating with the following techniques [21]:

1. RTL-based clock gate insertion on unmapped registers. Clock gating occurs when the register bank size meets certain minimum width constraints.

2. Gate-level clock gate insertion on both unmapped and previously mapped registers. In this case, clock gating is also applied to objects such as IP cores that are already mapped.

3. Power-driven gate-level clock gate insertion, which allows for further power optimizations because all aspects of power savings, such as switching activity and the flip-flop types to which the registers are mapped, are considered.

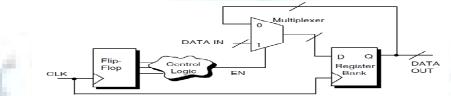

Without clock gating, Design Compiler implements register banks by using a feedback loop and a multiplexer. When such registers maintain the same value through multiple cycles, they use power unnecessarily.

#### FIG. 9: SHOWS A SIMPLE REGISTER BANK IMPLEMENTATION USING A MULTIPLEXER AND A FEEDBACK LOOP

Fig 9: Synchronous Load-Enable Register With Multiplexer.

The multiplexer also consumes power. Clock gating eliminates the feedback net and multiplexer shown in Fig.9 by inserting a 2-input gate in the clock net of the register. Clock gating can insert inverters or buffers to satisfy timing or clock waveform polarity requirements. The 2-input clock gate selectively prevents clock edges, thus preventing the gated-clock signal from clocking the gated register.

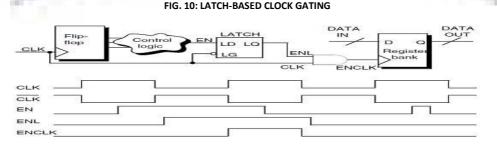

Fig. 10 shows a latch-based clock-gating style using a 2-input AND gate, however, depending on the type of register and the gating style, gating can use NAND, OR, and NOR gates instead.

INTERNATIONAL JOURNAL OF RESEARCH IN COMPUTER APPLICATION & MANAGEMENT A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories http://ijrcm.org.in/

### VOLUME NO. 2 (2012), ISSUE NO. 12 (DECEMBER)

Clock gating reduces the clock network power dissipation, relaxes the datapath timing, and reduces routing congestion by eliminating feedback multiplexer loops. For designs that have large multi-bit registers, clock gating can save power and reduce the number of gates in the design. However, for smaller register banks, the overhead of adding logic to the clock tree might not compare favorably to the power saved by eliminating a few feedback nets and multiplexers.

| TABLE 1: COMPARATIVE RESULTS OF PROPOSED ROUTER WITH EXISTING ROUTER DE | SIGN |

|-------------------------------------------------------------------------|------|

|-------------------------------------------------------------------------|------|

| TABLE 1. COMPARATIVE RESOLITS OF THOUGHED HOUTER WITH EXISTING HOUTER DESIGN |           |                   |       |                   |            |          |             |            |

|------------------------------------------------------------------------------|-----------|-------------------|-------|-------------------|------------|----------|-------------|------------|

| Network                                                                      | Topology  | Flit Size in bits | Ports | Buf Size in flits | Tech in nm | L in Clk | A in Sq.mm  | F in MHz   |

| Teraflops                                                                    | Mesh      | 32                | 4     | 16                | 65         | 5        | 0.34        | 4270       |

| Xpipes                                                                       | Custom    | 32                | 4     |                   | 100        | 7        |             |            |

| Dally                                                                        | Torus     | 256               | 5     | 4                 | 100        | 3        |             | 200 - 2000 |

| НІВІ                                                                         | Bus       | 32                | 2     | 2,8               | 130        | 4        | 0.03 -0.05  | 435        |

| Octagon                                                                      | Ext. Ring | 32                | 4     | 2,8               | 130        | 4        | 0.04 - 0.09 | 435        |

| SPIN                                                                         | Fat- T    | 16                | 8     | 8                 | 130        |          | 0.24        | 200        |

| Aethereal                                                                    | Mesh      | 96                | 5     | 8                 | 120        |          | 0.26        | 500        |

| ANoC                                                                         | Mesh      | 32                |       |                   | 130        |          | 0.25        | 500        |

| Mango                                                                        | Mesh      | 32                | 5     | 1                 |            |          | 0.19        | 795        |

| Hermes                                                                       | Mesh      | 32                | 5     | 2,8               | 130        | 10       | 0.05-0.11   | 435        |

| SoCBus                                                                       | Custom    | 16                | 3     | 1                 | 180        |          |             |            |

| ASoC                                                                         | Mesh      | 32                | 4     | 2                 | 180        |          | 0.04-0.08   | 400        |

| Avg.                                                                         |           | 50.1              | 4.8   | 6.4               | 170        | 5.2      | 0.14-0.22   | 328-596    |

| Present Work                                                                 | Mesh      | 32                | 4     | 8                 | 90         | 4        | 0.15        | 500        |

Legends used in above Table:-, Buf.-Buffer, Tech-Technology, L-Latency, A-Area, F-Frequency, Ext-Extended, R-Ring, , T-Tree Cus- Custom, Avg-Average, Pre-

### 8. EXPERIMENTAL RESULTS 1: PHYSICAL IMPLEMENTATION

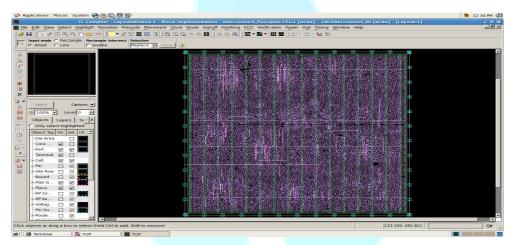

8.1.4x4 Routing Nodes D Flip Flop (DFF) \_Physical implementation:

8.2.4x4 Routing Node (SRAM)\_Physical implementation

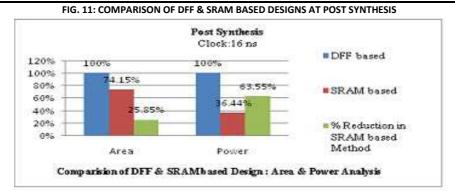

TABLE 2: COMPARISONS SHOWING RESULT OF AREA, POWER OF 4X4 ROUTING NODE AT POST SYNTHESIS # Clock Period: 16ns.

| Post Synthesis | DFF based    | SRAM based   | % Reduction in SRAM based Method |

|----------------|--------------|--------------|----------------------------------|

| Area           | 202704 sq um | 150314 sq um | 25.85%                           |

| Power          | 10.7 mW      | 3.9 mW       | 63.55%                           |

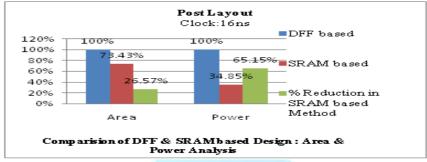

TABLE 3: COMPARISONS SHOWING RESULTS OF AREA, POWER OF 4X4 ROUTING NODE AT POST LAYOUT # Clock Period: 16ns.

| Post Layout | DFF based    | SRAM based   | % Reduction in SRAM based Method |

|-------------|--------------|--------------|----------------------------------|

| Area        | 205298 sq um | 150756 sq um | 26.567%                          |

| Power       | 14.29 mW     | 4.98 mW      | 65.15%                           |

INTERNATIONAL JOURNAL OF RESEARCH IN COMPUTER APPLICATION & MANAGEMENT A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories <u>http://ijrcm.org.in/</u>

65

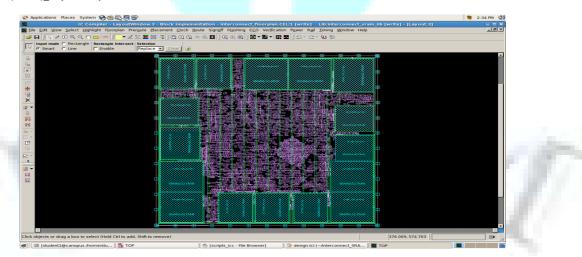

FIG. 12: COMPARISON OF DFF & SRAM BASED DESIGNS AT POST LAYOUT

### 9. INSERTION OF CLOCK GATING TECHNIQUES

9.1. INSERTING CLOCK GATES IN GATE-LEVEL DESIGN

To insert clock gating logic in gate-level netlist and to re-synthesize the design with the clock gating logic at Gate Level Netlist: 1. Read the gate-level netlist.

2. Use the compile ultra gate of

2. Use the compile\_ultra -gate\_clock command to compile your design. To apply this method, the compiler executes the following tcl commands:

# Optional setting

read\_ddc interconnect.ddc compile\_ultra -incremental -gate\_clock -scan insert\_dft report\_clock\_gating report\_power

### **10. EXPERIMENTAL RESULTS 2: USING CLOCK GATING TECHNIQUES**

10.1 POWER ANALYSIS AT GATE LEVEL

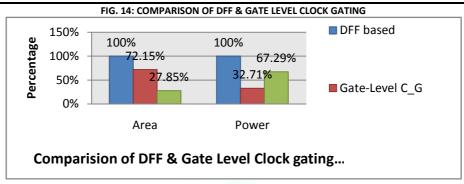

10.2. COMPARISONS CHART SHOWING RESULT OF AREA & POWER # Clock Period: 16 ns

### FIG. 13: COMPARISON OF DFF & GATE LEVEL CLOCK GATING

| DFF based         |         | Gate-Level C_G |  |  |

|-------------------|---------|----------------|--|--|

| Area 202704 Sq um |         | 146254 Sq um   |  |  |

| Power             | 10.7 mW | 3.50 mW        |  |  |

### **11. CONCLUSION**

2D-Mesh has been an area efficient implementation of a routing node for an NOC is demonstrated. Of the four components of routing node, the input block (mainly consisting of buffers) and scheduler have been modified to save area requirements. The other two components of the routing node take up negligible area in comparison. The use of custom SRAM in place of synthesizable flip flops in the input block has resulted in a saving of over 26% of the silicon area and power optimization is 65% when operated at 16 ns clock.

Clock gating is an important high-level technique for reducing the power consumption of a design. Clock gating reduces the clock network power dissipation, relaxes the datapath timing, and reduces routing congestion by eliminating feedback multiplexer loops. For designs that have large multi-bit registers, clock gating gate level can save power and reduce the number of gates in the design. In our design case, it has been further observed that the power optimization with clock gating techniques at gate level saves 67.38%, of power while 32.62 %, 32.71 % & 30.28% silicon area has been saved.

### **12. FUTURE SCOPE**

The existing design has been synthesized using MUX as a crossbar switch more Area efficient crossbar like tristate and sense amps can further make the design efficient.

We foresee that Area & Power of existing design can be further optimized by Low Power Design Methodology Likes:

1. Multi VDD - Since dynamic power is proportional to VDD<sup>2</sup> lowering VDD on selected blocks helps reduce power significantly. Unfortunately, lowering the voltage also increases the delay of the gates in the design.

2. Multi Threshold Logic- As geometries have shrunk to 130nm, 90nm, and below, using libraries with multiple V<sub>T</sub> has become a more efficient way of reducing leakage voltage.

### **13. REFERENCES**

- 1. ARTISAN "A comparison of network-on-chip and busses, "white paper, (2005).

- 2. C. A. Zeferino and A. A. Susin, "SocIN: A parametric and scalable network-on- chip", Proc. 16th Symposium on Integrated Circuits and Systems Design, pp. 169-175, (2003).

- 3. C. Wang et al, "Area and power efficient innovative NoC Architecture", Proc. of 18<sup>th</sup>EuroMicro International Conference, PDP 2010, Pisa, Italy, (2010).

- 4. E. Beigne, "An asynchronous NOC architecture is providing low latency service and its multi-level design framework", in ASYNC, Mar., pp. 54–63. (2005)

- 5. E. Bolotin, A. Morgenshtein, I. Cidon, R. Ginosar, and A. Kolodny, "Automatic hardware-efficient SoC integration by QoS Network-on-Chip", Proc. 11th International IEEE Conference on Electronics, Circuits and Systems, pp. 479-482, (2004).

- 6. E. Bolotin, I. Cidon, R. Ginosar and A. Kolodny, "Cost considerations in Network on Chip Integration", The VLSI Journal, no. 38, , pp. 19-42. (2004)

- E. Bolotin, I. Cidon, R. Ginosar, and A. Kolodny, "QNoC: QoS architecture and design process for network on chip", Journal of Systems Architecture, Volume 50, Issue 2-3 (Special Issue on Network on Chip), pp. 105-128, February (2004).

- 8. H. Zimmer, S. Zink, T. Hollstein, and M. Glesner, "Buffer-architecture exploration for routers in a hierarchical network-on-chip," Proc. 19th IEEE International Symposium on Parallel and Distributed Processing, pp., 1-4, April (2005).

- 9. J. Owens et al., "Research challenges for on-chip interconnection networks", IEEE Micro, vol. 27, no. 5, pp. 96–108, Sep-Oct. (2007).

- Khalid latif, Tiburiu Seceleanu & hannu Tenhunen "Power and Area Efficient Design of Network-on-Chip Router through Utilization of Ideal Buffer". Proc.17<sup>th</sup> IEEE International Conference and workshop on Engineering of Computer based System. (2010).

- 11. L. Benini and G. de Micheli, "Networks on chips: A new SoC paradigm", IEEE Computer, vol. 35, no. 1, pp. 70–78, Jan. (2002).

- 12. Luca Benini and Giovanni De Micheli," Networks on Chips, Morgan "Kaufmann Publishers (2006).

- 13. Michael Keating, David Flynn, Rob Aitken, Alan Gibbons, and Kaijian Shi, "Low Power Methodology Manual: For System-on-Chip Design" Springer, (2007).

- 14. Michael, Keating "The Future of Low Power", SNUG, (2007),

- 15. N. Banerjee, P. Vellanki and K.S. Chatha. "A Power and Performance Model for Network-on-Chip Architectures". Proc. of the conference on Design, automation and test in Europe (DATE), pp.1250-1255 (2004), Vol.2,

- 16. "Power Compiler User Guide", SYNOPSIS Version F 2011.9, December (2011).

- 17. Saastamoinen, M. Alho, and J. Nurmi, "Buffer implementation for Proteome network-on-chip", International IEEE Proceeding on Circuits and Systems, vol. 2, pp. 113-116, May (2003).

- 18. Sudhir N, Shelke ,Pramod B Patil "Impact of SoC Low Power Design, Power Management Techniques & Physical Challenges "International Journal of Electrical, Electronics & Computing Technology (IJEECT), Vol1,Issue2,Jan-Apr (2011)

- 19. T. Bartic, "Topology adaptive network-on-chip design and implementation", IEEE Proc. Comput. Digit Tech., vol. 152, no. 4, pp. 467–472, Jul. (2005).

- 20. T. Bjerregaard and J Sparose, "A router architecture for connection oriented service guarantees in the MANGO clockless network-on-chip", in DATE, vol. 2, p p. 1226-1231. Mar. (2005)

- 21. T. Bjerregaard and S. Mahadevan, "A survey of research and practices of network-on-chip, ACM Computing Surveys", vol. 38, no. 1, p. article No. 1, Jun. (2006).

- 22. W. Hangsheng, L. S. Peh, and S. Malik." Power- driven design of router micro architectures in on-chip networks". Proc. of the 36th Annual IEEE/ACM International Symposium on Micro architecture (MI-CRO), pp. 105-116, (2003).

- 23. W. J. Dally and B. Towles, "Principles and practices of interconnection networks", Morgan Kaufmann Publishers, (2004).

- 24. Xuning Chen and Li-ShiuanPeh, "Leakage power modeling and optimization of interconnection net- works." Proc. of International Symposium on Low Power Electronics and Design, pp. 9095, (2003).

# REQUEST FOR FEEDBACK

### **Dear Readers**

At the very outset, International Journal of Research in Computer Application and Management (IJRCM) acknowledges & appreciates your efforts in showing interest in our present issue under your kind perusal.

I would like to request you to supply your critical comments and suggestions about the material published in this issue as well as on the journal as a whole, on our E-mail **infoijrcm@gmail.com** for further improvements in the interest of research.

If you have any queries please feel free to contact us on our E-mail infoijrcm@gmail.com.

I am sure that your feedback and deliberations would make future issues better – a result of our joint effort.

Looking forward an appropriate consideration.

With sincere regards

Thanking you profoundly

Academically yours

Sd/-

**Co-ordinator**

## **ABOUT THE JOURNAL**

In this age of Commerce, Economics, Computer, I.T. & Management and cut throat competition, a group of intellectuals felt the need to have some platform, where young and budding managers and academicians could express their views and discuss the problems among their peers. This journal was conceived with this noble intention in view. This journal has been introduced to give an opportunity for expressing refined and innovative ideas in this field. It is our humble endeavour to provide a springboard to the upcoming specialists and give a chance to know about the latest in the sphere of research and knowledge. We have taken a small step and we hope that with the active cooperation of like-minded scholars, we shall be able to serve the society with our humble efforts.

Our Other Fournals

OF RESE

ATIONAL JOURNAL COMMERCE & MA

INTERNATIONAL JOURNAL OF RESEARCH IN COMPUTER APPLICATION & MANAGEMENT A Monthly Double-Blind Peer Reviewed (Refereed/Juried) Open Access International e-Journal - Included in the International Serial Directories http://ijrcm.org.in/

П